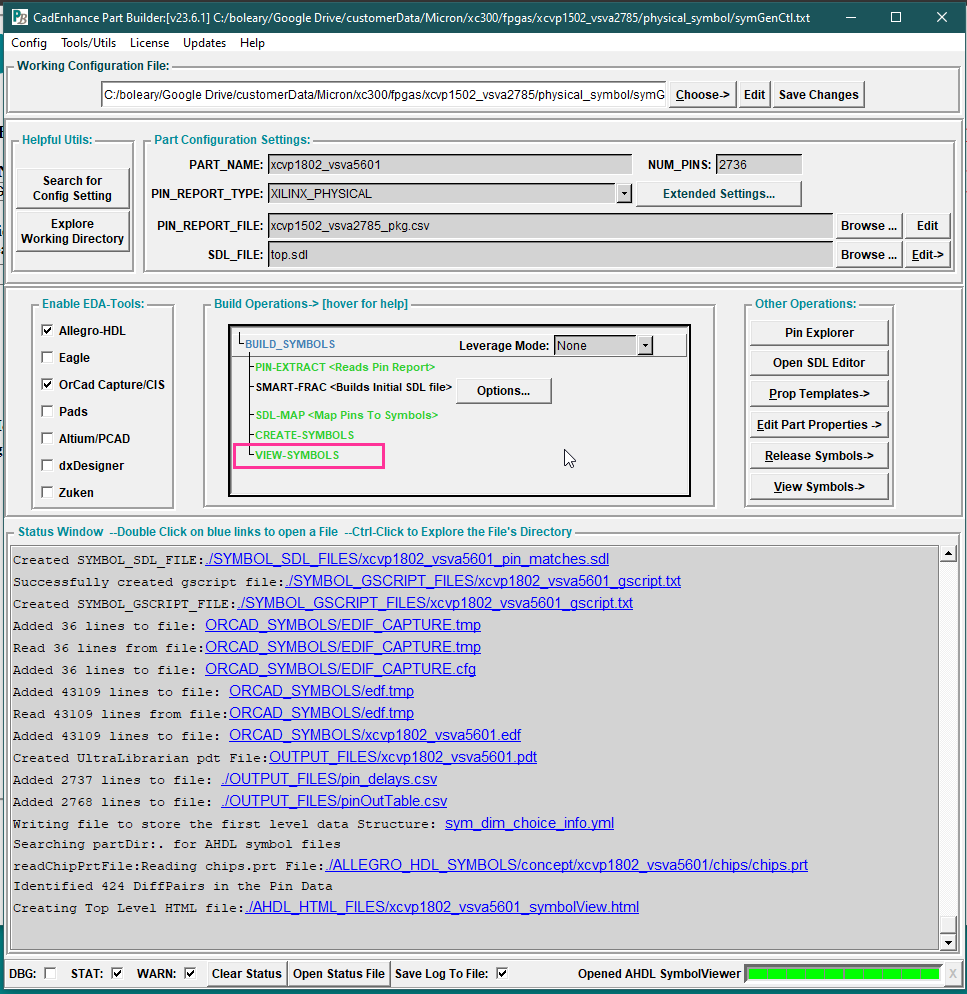

The latest v23.6.1 release features a Streamlined UI refresh for PartBuilder and vastly Improved Configuration Widgets for NetBom

Read MoreThe Cadence® Allegro Design Authoring™ Schematic Capture Tool is quite a very powerful Tool, but it can be intimidating to first time users.

It's deceptive in its simplicity, and there are many hidden features even a grizzly old veteran can learn if they take the time to look for new tricks.

Here we share a FREE e-Book and video channel, detailing six useful “Hacks” to help you save countless days in your design cycles.

AI has made this a very exciting time for software developers… At cadEnhance, tools like ChatGPT, TabNine, and GitHub Copilot can help write our code and documentation for us. In welcoming 2023, we should explore and embrace the capabilities of Automated tools, or we may find ourselves left in the dust by our competitors.

Read MoreIn today's designs containing FPGAs with thousands of pins, a tool to verify your FPGA connectivity is a real necessity. NetBom's Interactive End Point Verify Technology makes this unpleasant job quick, reliable, repeatable and almost bearable.

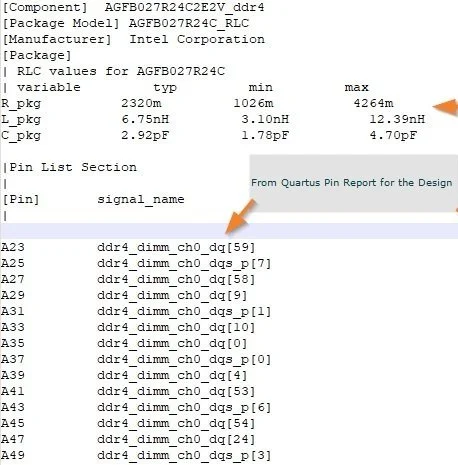

Read MoreFPGA vendors like Intel®, Xilinx®, Lattice® and MicroChip® provide tools to create a design specific IBIS model, but support for these tools sometimes lags behind the release and delivery of the actual device in the design software. Intel’s Latest AgileX devices fall into that case. The creation of design specific IBIS model for these new giant FPGA devices, some with >3000 pins, are not yet supported by the Intel Quartus Tool.

To bridge this gap, we have added the capability to create the design specific IBIS models for AgileX and other Intel FGPA families to our FpgaPinPlanner Tool.

Read MoreThe collection of videos below highlight some build examples, and highlights the advantage PartBuilder brings to the table when creating symbols for Xilinx and Intel/Altera FPGAs. They demonstrate how PartBuilder creates the ASCII versions of Zuken symbol files without requiring or consuming a Zuken License or Install.

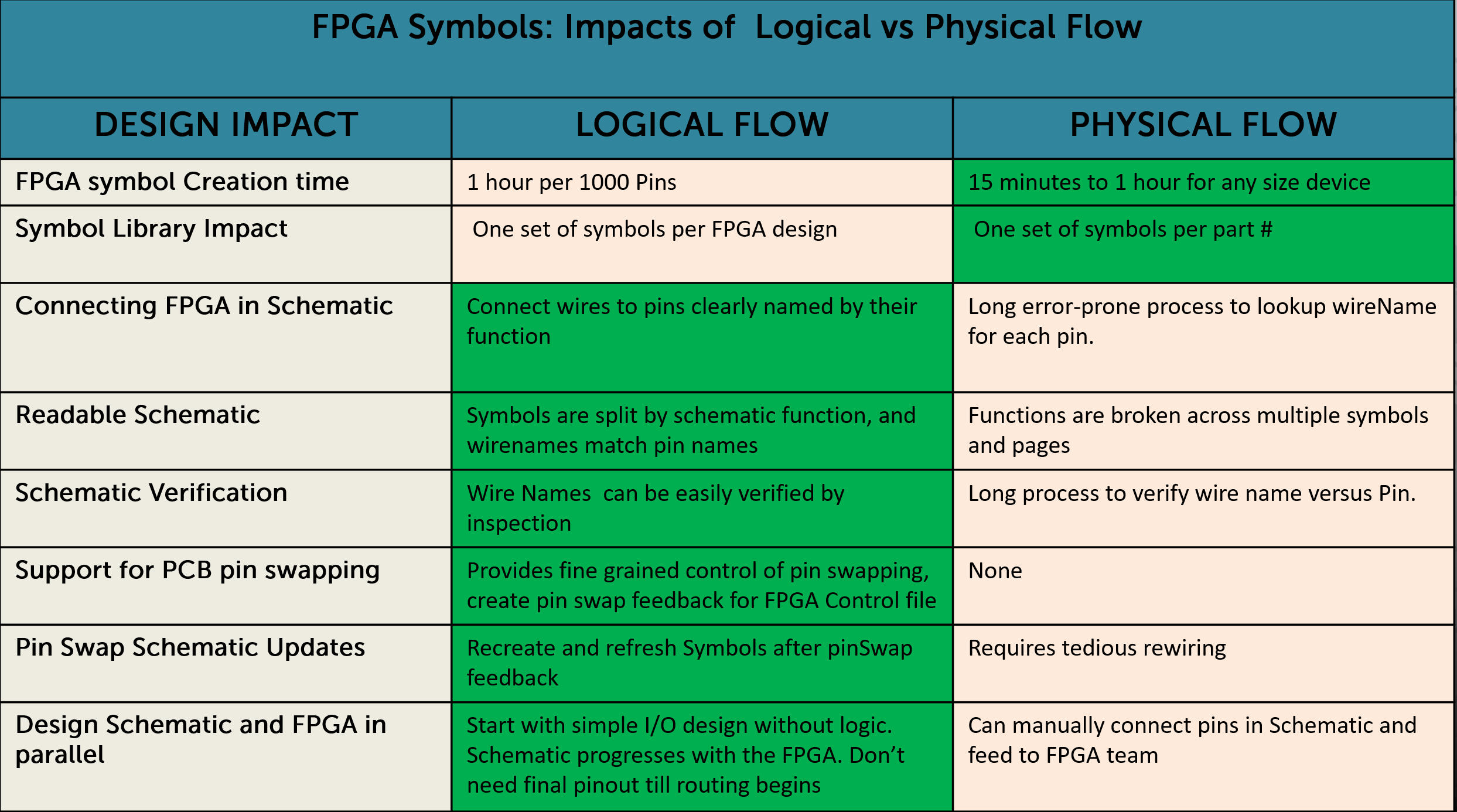

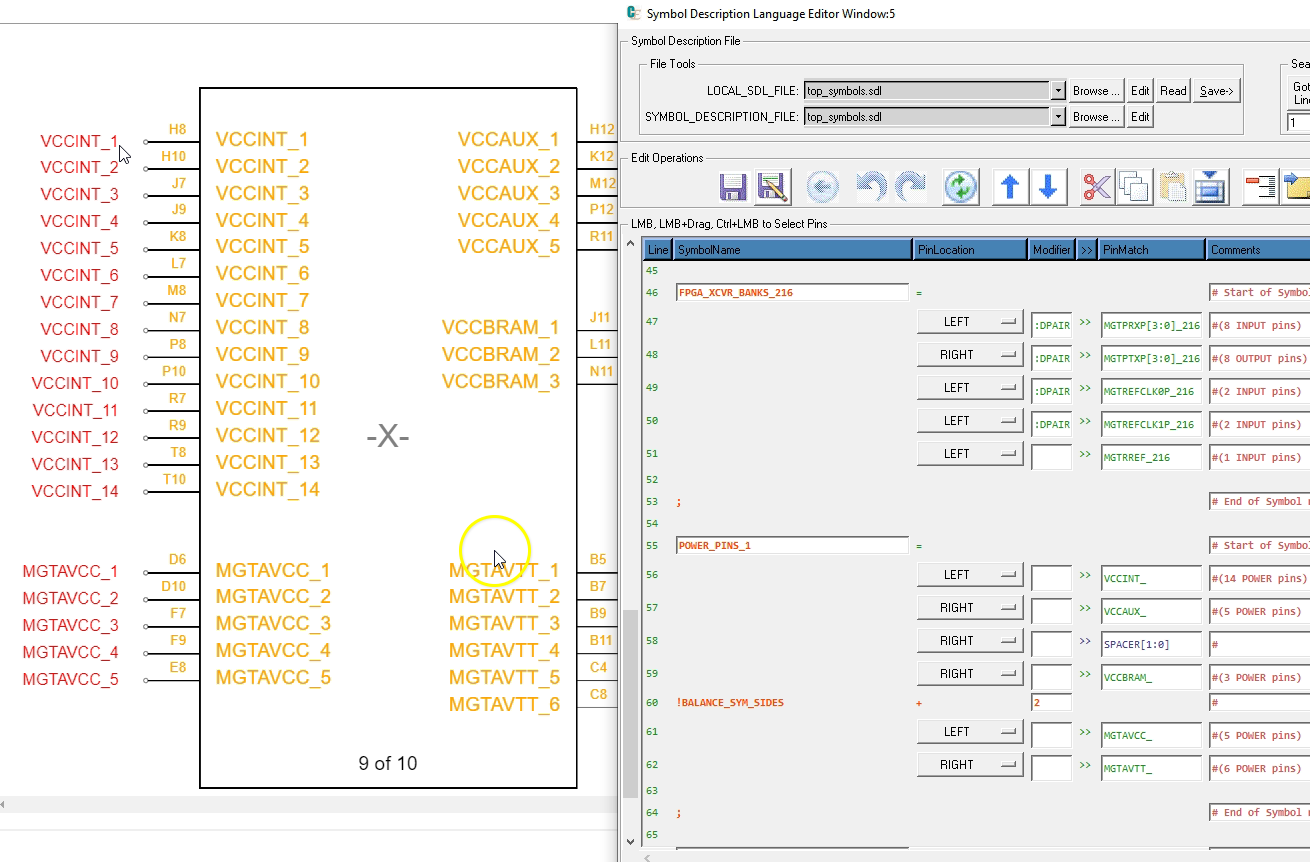

Read MorePartBuilder uses built in FPGA intelligence to quickly and accurately divide parts into interchangeable functional symbol blocks making it easy to work with in the schematic. The Symbol Description Language (SDL) enables easy manipulation to create the final symbol set you need, instead of forcing you to use one generic solution.

Read MoreBuilding accurate schematic symbols for high pin count devices is one of the most mind-numbing, time-consuming, frustrating pieces of the designer’s job. Naturally, as engineers, we want to cheat. The more we can automate the process, the more time we can spend on more interesting problems.

Read MorePin counts are exploding. Devices with 4000-8000+ pins are now common offerings of the large FPGA and Network IC vendors. How do you plan to build schematic symbols for such a behemoth?

Read MoreBefore the CadEnhance PartBuilder tool was created, the creation of complex multi-section FPGA symbols was quite a chore, and usually fell to a collaboration between the Board Engineer and the Part Librarian.

Read MoreHere we examine the process used to create a high Pin Count device from Xilinx part Data using the CadEnhance Part Builder Tool. The Part Builder tool is designed to get accurate pin information from a variety of sources.

Read More