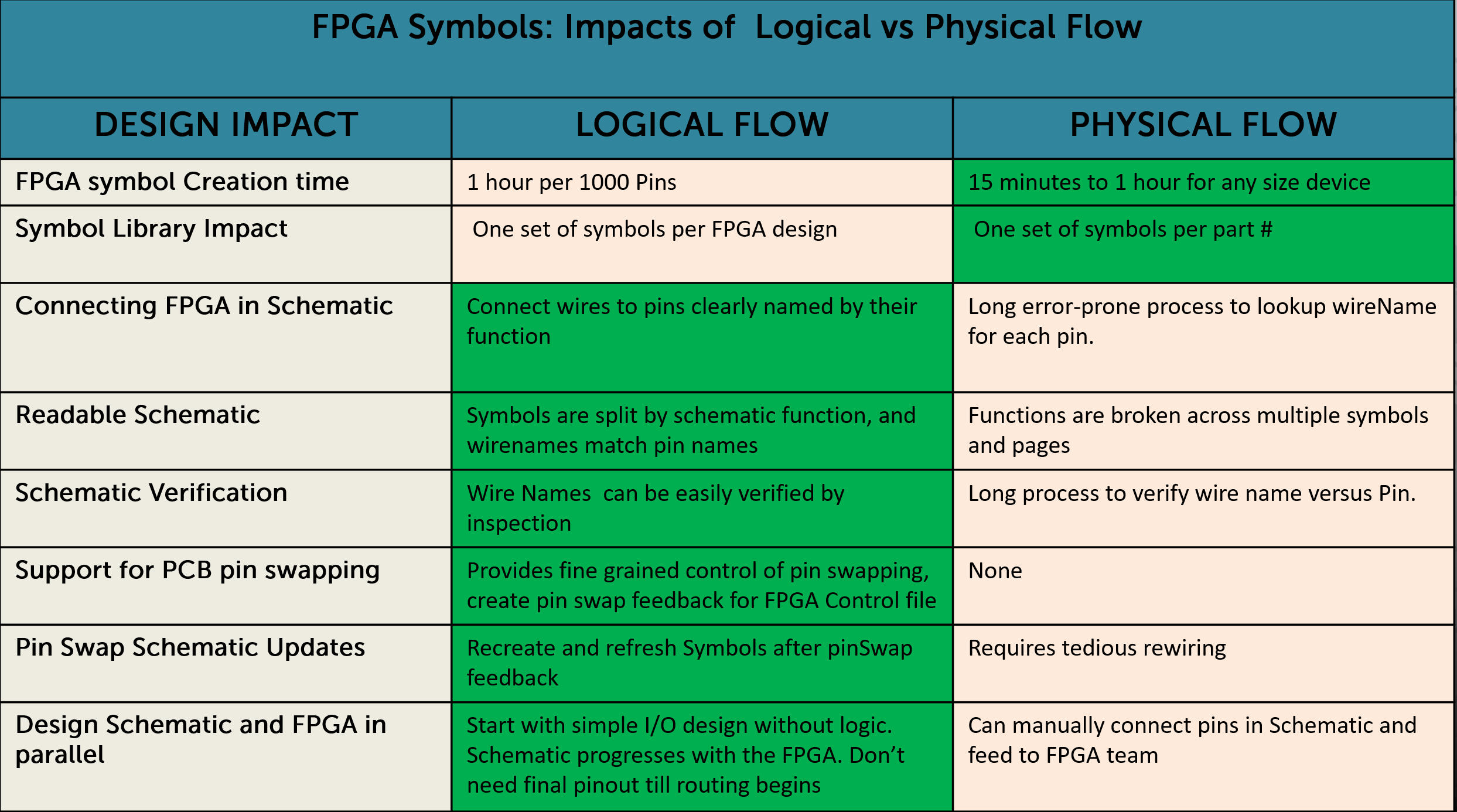

Pin counts are exploding. Devices with 4000-8000+ pins are now common offerings of the large FPGA and Network IC vendors. How do you plan to build schematic symbols for such a behemoth?

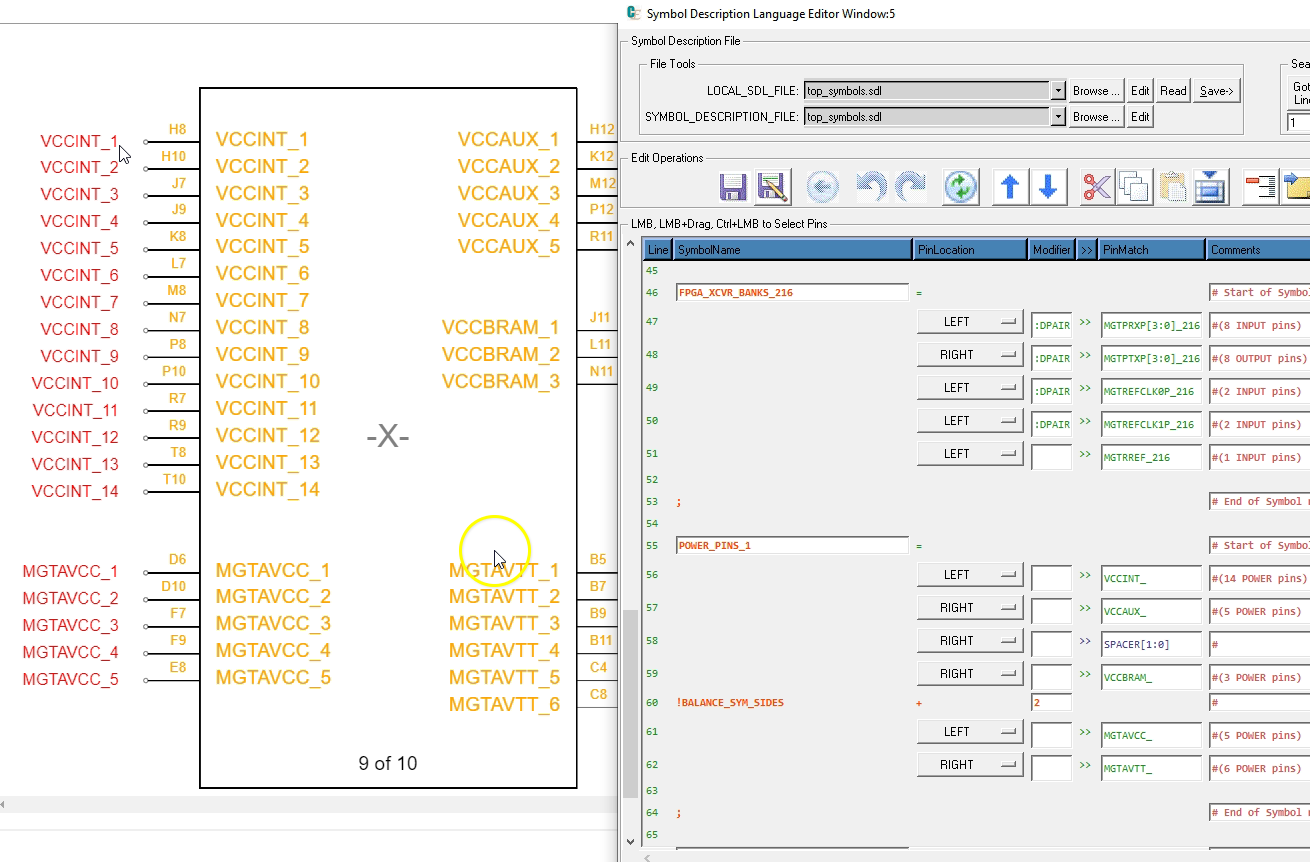

Read MoreBefore the CadEnhance PartBuilder tool was created, the creation of complex multi-section FPGA symbols was quite a chore, and usually fell to a collaboration between the Board Engineer and the Part Librarian.

Read MoreHere we examine the process used to create a high Pin Count device from Xilinx part Data using the CadEnhance Part Builder Tool. The Part Builder tool is designed to get accurate pin information from a variety of sources.

Read More